[

{

"path": ".github/workflows/arduino_ci.yml",

"content": "name: Arduino_CI\n\non:\n push:\n branches: [ master, develop ]\n pull_request:\n branches: [ master, develop ]\n\njobs:\n arduino_ci:\n runs-on: ubuntu-latest\n strategy:\n fail-fast: false\n steps:\n - uses: actions/checkout@v2\n - name: install script\n run: |\n source <(curl -SLs https://raw.githubusercontent.com/ROBOTIS-GIT/OpenCR/master/install.sh) ${{github.ref}}\n build_platform opencr"

},

{

"path": ".gitignore",

"content": "# Compiled Object files\n*.slo\n*.lo\n*.o\n\n# Precompiled Headers\n*.gch\n*.pch\n\n# Compiled Dynamic libraries\n*.so\n*.dylib\n*.dll\n\n# Fortran module files\n*.mod\n\n# Compiled Static libraries\n*.lai\n*.la\n*.a\n*.lib\n\n# Executables\n*.exe\n*.out\n*.app\n\n.vscode\n.metadata"

},

{

"path": ".project",

"content": "\n\n\tOpenCR\n\t\n\t\n\t\n\t\n\t\n\t\n\t\n\n"

},

{

"path": "49-stlinkv2.rules",

"content": "SUBSYSTEMS==\"usb\", ATTRS{idVendor}==\"0483\", ATTRS{idProduct}==\"3748\", MODE:=\"0666\", SYMLINK+=\"stlinkv2_%n\"\n"

},

{

"path": "99-opencr-cdc.rules",

"content": "#http://linux-tips.org/t/prevent-modem-manager-to-capture-usb-serial-devices/284/2.\n\n#cp rules /etc/udev/rules.d/\n#sudo udevadm control --reload-rules\n#sudo udevadm trigger\n\nATTRS{idVendor}==\"0483\" ATTRS{idProduct}==\"5740\", ENV{ID_MM_DEVICE_IGNORE}=\"1\", MODE:=\"0666\"\nATTRS{idVendor}==\"0483\" ATTRS{idProduct}==\"df11\", MODE:=\"0666\"\nATTRS{idVendor}==\"fff1\" ATTRS{idProduct}==\"ff48\", ENV{ID_MM_DEVICE_IGNORE}=\"1\", MODE:=\"0666\"\nATTRS{idVendor}==\"10c4\" ATTRS{idProduct}==\"ea60\", ENV{ID_MM_DEVICE_IGNORE}=\"1\", MODE:=\"0666\"\n"

},

{

"path": "LICENSE",

"content": " Apache License\n Version 2.0, January 2004\n http://www.apache.org/licenses/\n\n TERMS AND CONDITIONS FOR USE, REPRODUCTION, AND DISTRIBUTION\n\n 1. Definitions.\n\n \"License\" shall mean the terms and conditions for use, reproduction,\n and distribution as defined by Sections 1 through 9 of this document.\n\n \"Licensor\" shall mean the copyright owner or entity authorized by\n the copyright owner that is granting the License.\n\n \"Legal Entity\" shall mean the union of the acting entity and all\n other entities that control, are controlled by, or are under common\n control with that entity. For the purposes of this definition,\n \"control\" means (i) the power, direct or indirect, to cause the\n direction or management of such entity, whether by contract or\n otherwise, or (ii) ownership of fifty percent (50%) or more of the\n outstanding shares, or (iii) beneficial ownership of such entity.\n\n \"You\" (or \"Your\") shall mean an individual or Legal Entity\n exercising permissions granted by this License.\n\n \"Source\" form shall mean the preferred form for making modifications,\n including but not limited to software source code, documentation\n source, and configuration files.\n\n \"Object\" form shall mean any form resulting from mechanical\n transformation or translation of a Source form, including but\n not limited to compiled object code, generated documentation,\n and conversions to other media types.\n\n \"Work\" shall mean the work of authorship, whether in Source or\n Object form, made available under the License, as indicated by a\n copyright notice that is included in or attached to the work\n (an example is provided in the Appendix below).\n\n \"Derivative Works\" shall mean any work, whether in Source or Object\n form, that is based on (or derived from) the Work and for which the\n editorial revisions, annotations, elaborations, or other modifications\n represent, as a whole, an original work of authorship. For the purposes\n of this License, Derivative Works shall not include works that remain\n separable from, or merely link (or bind by name) to the interfaces of,\n the Work and Derivative Works thereof.\n\n \"Contribution\" shall mean any work of authorship, including\n the original version of the Work and any modifications or additions\n to that Work or Derivative Works thereof, that is intentionally\n submitted to Licensor for inclusion in the Work by the copyright owner\n or by an individual or Legal Entity authorized to submit on behalf of\n the copyright owner. For the purposes of this definition, \"submitted\"\n means any form of electronic, verbal, or written communication sent\n to the Licensor or its representatives, including but not limited to\n communication on electronic mailing lists, source code control systems,\n and issue tracking systems that are managed by, or on behalf of, the\n Licensor for the purpose of discussing and improving the Work, but\n excluding communication that is conspicuously marked or otherwise\n designated in writing by the copyright owner as \"Not a Contribution.\"\n\n \"Contributor\" shall mean Licensor and any individual or Legal Entity\n on behalf of whom a Contribution has been received by Licensor and\n subsequently incorporated within the Work.\n\n 2. Grant of Copyright License. Subject to the terms and conditions of\n this License, each Contributor hereby grants to You a perpetual,\n worldwide, non-exclusive, no-charge, royalty-free, irrevocable\n copyright license to reproduce, prepare Derivative Works of,\n publicly display, publicly perform, sublicense, and distribute the\n Work and such Derivative Works in Source or Object form.\n\n 3. Grant of Patent License. Subject to the terms and conditions of\n this License, each Contributor hereby grants to You a perpetual,\n worldwide, non-exclusive, no-charge, royalty-free, irrevocable\n (except as stated in this section) patent license to make, have made,\n use, offer to sell, sell, import, and otherwise transfer the Work,\n where such license applies only to those patent claims licensable\n by such Contributor that are necessarily infringed by their\n Contribution(s) alone or by combination of their Contribution(s)\n with the Work to which such Contribution(s) was submitted. If You\n institute patent litigation against any entity (including a\n cross-claim or counterclaim in a lawsuit) alleging that the Work\n or a Contribution incorporated within the Work constitutes direct\n or contributory patent infringement, then any patent licenses\n granted to You under this License for that Work shall terminate\n as of the date such litigation is filed.\n\n 4. Redistribution. You may reproduce and distribute copies of the\n Work or Derivative Works thereof in any medium, with or without\n modifications, and in Source or Object form, provided that You\n meet the following conditions:\n\n (a) You must give any other recipients of the Work or\n Derivative Works a copy of this License; and\n\n (b) You must cause any modified files to carry prominent notices\n stating that You changed the files; and\n\n (c) You must retain, in the Source form of any Derivative Works\n that You distribute, all copyright, patent, trademark, and\n attribution notices from the Source form of the Work,\n excluding those notices that do not pertain to any part of\n the Derivative Works; and\n\n (d) If the Work includes a \"NOTICE\" text file as part of its\n distribution, then any Derivative Works that You distribute must\n include a readable copy of the attribution notices contained\n within such NOTICE file, excluding those notices that do not\n pertain to any part of the Derivative Works, in at least one\n of the following places: within a NOTICE text file distributed\n as part of the Derivative Works; within the Source form or\n documentation, if provided along with the Derivative Works; or,\n within a display generated by the Derivative Works, if and\n wherever such third-party notices normally appear. The contents\n of the NOTICE file are for informational purposes only and\n do not modify the License. You may add Your own attribution\n notices within Derivative Works that You distribute, alongside\n or as an addendum to the NOTICE text from the Work, provided\n that such additional attribution notices cannot be construed\n as modifying the License.\n\n You may add Your own copyright statement to Your modifications and\n may provide additional or different license terms and conditions\n for use, reproduction, or distribution of Your modifications, or\n for any such Derivative Works as a whole, provided Your use,\n reproduction, and distribution of the Work otherwise complies with\n the conditions stated in this License.\n\n 5. Submission of Contributions. Unless You explicitly state otherwise,\n any Contribution intentionally submitted for inclusion in the Work\n by You to the Licensor shall be under the terms and conditions of\n this License, without any additional terms or conditions.\n Notwithstanding the above, nothing herein shall supersede or modify\n the terms of any separate license agreement you may have executed\n with Licensor regarding such Contributions.\n\n 6. Trademarks. This License does not grant permission to use the trade\n names, trademarks, service marks, or product names of the Licensor,\n except as required for reasonable and customary use in describing the\n origin of the Work and reproducing the content of the NOTICE file.\n\n 7. Disclaimer of Warranty. Unless required by applicable law or\n agreed to in writing, Licensor provides the Work (and each\n Contributor provides its Contributions) on an \"AS IS\" BASIS,\n WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or\n implied, including, without limitation, any warranties or conditions\n of TITLE, NON-INFRINGEMENT, MERCHANTABILITY, or FITNESS FOR A\n PARTICULAR PURPOSE. You are solely responsible for determining the\n appropriateness of using or redistributing the Work and assume any\n risks associated with Your exercise of permissions under this License.\n\n 8. Limitation of Liability. In no event and under no legal theory,\n whether in tort (including negligence), contract, or otherwise,\n unless required by applicable law (such as deliberate and grossly\n negligent acts) or agreed to in writing, shall any Contributor be\n liable to You for damages, including any direct, indirect, special,\n incidental, or consequential damages of any character arising as a\n result of this License or out of the use or inability to use the\n Work (including but not limited to damages for loss of goodwill,\n work stoppage, computer failure or malfunction, or any and all\n other commercial damages or losses), even if such Contributor\n has been advised of the possibility of such damages.\n\n 9. Accepting Warranty or Additional Liability. While redistributing\n the Work or Derivative Works thereof, You may choose to offer,\n and charge a fee for, acceptance of support, warranty, indemnity,\n or other liability obligations and/or rights consistent with this\n License. However, in accepting such obligations, You may act only\n on Your own behalf and on Your sole responsibility, not on behalf\n of any other Contributor, and only if You agree to indemnify,\n defend, and hold each Contributor harmless for any liability\n incurred by, or claims asserted against, such Contributor by reason\n of your accepting any such warranty or additional liability.\n\n END OF TERMS AND CONDITIONS\n\n APPENDIX: How to apply the Apache License to your work.\n\n To apply the Apache License to your work, attach the following\n boilerplate notice, with the fields enclosed by brackets \"{}\"\n replaced with your own identifying information. (Don't include\n the brackets!) The text should be enclosed in the appropriate\n comment syntax for the file format. We also recommend that a\n file or class name and description of purpose be included on the\n same \"printed page\" as the copyright notice for easier\n identification within third-party archives.\n\n Copyright {yyyy} {name of copyright owner}\n\n Licensed under the Apache License, Version 2.0 (the \"License\");\n you may not use this file except in compliance with the License.\n You may obtain a copy of the License at\n\n http://www.apache.org/licenses/LICENSE-2.0\n\n Unless required by applicable law or agreed to in writing, software\n distributed under the License is distributed on an \"AS IS\" BASIS,\n WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.\n See the License for the specific language governing permissions and\n limitations under the License.\n"

},

{

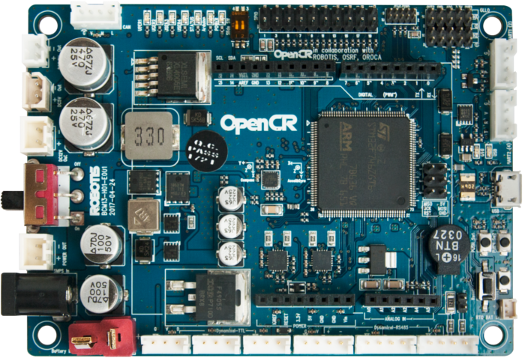

"path": "README.md",

"content": "# OpenCR: Open Source Control Module for ROS [](https://travis-ci.org/ROBOTIS-GIT/OpenCR/)\n\n\n## ROBOTIS e-Manual for OpenCR\n- [ROBOTIS e-Manual for OpenCR](http://emanual.robotis.com/docs/en/parts/controller/opencr10/)\n\n## Open Source related to OpenCR\n- [Micro ROS Arduino](https://github.com/micro-ROS/micro_ros_arduino)\n- [OpenCR](https://github.com/ROBOTIS-GIT/OpenCR)\n- [OpenCR-Hardware](https://github.com/ROBOTIS-GIT/OpenCR-Hardware)\n- [OpenCM 9.04](https://github.com/ROBOTIS-GIT/OpenCM9.04)\n- [dynamixel_sdk](https://github.com/ROBOTIS-GIT/DynamixelSDK)\n- [turtlebot3](https://github.com/ROBOTIS-GIT/turtlebot3)\n- [open_manipulator](https://github.com/ROBOTIS-GIT/open_manipulator)\n- [robotis_op3](https://github.com/ROBOTIS-GIT/ROBOTIS-OP3)\n\n## Documents and Videos related to OpenCR\n- [ROBOTIS e-Manual for OpenCR](http://emanual.robotis.com/docs/en/parts/controller/opencr10/)\n- [ROBOTIS e-Manual for OpenCM 9.04](http://emanual.robotis.com/docs/en/parts/controller/opencm904/)\n- [ROBOTIS e-Manual for OpenCM 485 Expansion Board](http://emanual.robotis.com/docs/en/parts/controller/opencm485exp/)\n- [ROBOTIS e-Manual for Dynamixel SDK](http://emanual.robotis.com/docs/en/software/dynamixel/dynamixel_sdk/overview/)\n- [ROBOTIS e-Manual for TurtleBot3](http://turtlebot3.robotis.com/)\n- [ROBOTIS e-Manual for OpenManipulator](http://emanual.robotis.com/docs/en/platform/openmanipulator/)\n- [ROBOTIS e-Manual for ROBOTIS OP3](http://emanual.robotis.com/docs/en/platform/op3/introduction/)\n- [Videos for OpenCR](https://www.youtube.com/playlist?list=PLRG6WP3c31_VTd-u90LVXaT1B8NMjCSoj)\n\n## Repository folder structure description\n- arduino\n - opencr_arduino\n - libraries : A collection of some libraries that can be used with OpenCR.\n - opencr : OpenCR package core to be installed in Arduino.\n - tools : Tools for OpenCR firmware writing.\n - opencr_develop\n - opencr_bootloader : OpenCR bootloader source\n - opencr_ld : OpenCR loader source (related bootloader)\n - opencr_ld_shell : OpenCR loader script source for TB3\n - opencr_release\n - Folders(version name) : Compressed files for updating TB3 core binary with ld_shell for each TB3 core version.\n - shell_update : Latest Compressed files for updating TB3 core binary with ld_shell.\n - package_opencr_index.json : json file for Arduino OpenCR package.\n"

},

{

"path": "arduino/opencr_arduino/opencr/.gitignore",

"content": ".vscode\n"

},

{

"path": "arduino/opencr_arduino/opencr/boards.txt",

"content": "# OpenCR Boards\n#\nmenu.device_variant=Variant\nmenu.bootloader_version=Bootloader version\nmenu.upload_method=Upload method\n\nOpenCR.bootloader.tool = dfu_util\nOpenCR.bootloader.file = opencr_boot.bin\n\nOpenCR.name=OpenCR Board\nOpenCR.upload.maximum_size=786432\n\nOpenCR.upload.file_type=bin\nOpenCR.upload.ram.maximum_size=256788\nOpenCR.upload.flash.maximum_size=786432\nOpenCR.upload.params.quiet=no\n\nOpenCR.build.mcu=cortex-m7\nOpenCR.build.f_cpu=216000000L\nOpenCR.build.board=OpenCR\nOpenCR.build.core=arduino\nOpenCR.build.common_flags=-mthumb -DSTM32F746xx -D__OPENCR__\n\nOpenCR.build.ldscript=bsp/opencr/ldscript/opencr_flash.ld\nOpenCR.build.variant=OpenCR\nOpenCR.build.variant_system_lib=lib_f746.a\nOpenCR.build.extra_flags=\n\n\nOpenCR.build.inc1=bsp/opencr\nOpenCR.build.inc2=bsp/opencr/include\nOpenCR.build.inc3=hw\nOpenCR.build.inc4=hw/driver\nOpenCR.build.inc5=hw/usb_cdc\nOpenCR.build.inc6=lib/STM32F7xx_HAL_Driver/Inc/\nOpenCR.build.inc7=\n\n#OpenCR.upload.tool=opencr_ld\n#OpenCR.menu.upload_method.upload.tool=opencr_ld\n\nOpenCR.menu.upload_method.UploadMethod=OpenCR Bootloader\nOpenCR.menu.upload_method.UploadMethod.upload.protocol=opencr_ld\nOpenCR.menu.upload_method.UploadMethod.upload.tool=opencr_ld\n"

},

{

"path": "arduino/opencr_arduino/opencr/cores/arduino/Arduino.h",

"content": "/*\n Arduino.h - Main include file for the Arduino SDK\n Copyright (c) 2005-2013 Arduino Team. All right reserved.\n\n This library is free software; you can redistribute it and/or\n modify it under the terms of the GNU Lesser General Public\n License as published by the Free Software Foundation; either\n version 2.1 of the License, or (at your option) any later version.\n\n This library is distributed in the hope that it will be useful,\n but WITHOUT ANY WARRANTY; without even the implied warranty of\n MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU\n Lesser General Public License for more details.\n\n You should have received a copy of the GNU Lesser General Public\n License along with this library; if not, write to the Free Software\n Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA\n*/\n\n#ifndef Arduino_h\n#define Arduino_h\n\n#include \n#include \n#include \n#include \n\n\n// some libraries and sketches depend on this\n// AVR stuff, assuming Arduino.h or WProgram.h\n// automatically includes it...\n#include \n#include \n\n#include \"binary.h\"\n#include \"hw.h\"\n#include \"itoa.h\"\n\n#ifdef __cplusplus\nextern \"C\"{\n#endif // __cplusplus\n\n\n#include \"chip.h\"\n#include \"wiring_constants.h\"\n\n#define clockCyclesPerMicrosecond() ( SystemCoreClock / 1000000L )\n#define clockCyclesToMicroseconds(a) ( ((a) * 1000L) / (SystemCoreClock / 1000L) )\n#define microsecondsToClockCycles(a) ( (a) * (SystemCoreClock / 1000000L) )\n\nvoid yield(void);\n\n/* sketch */\nextern void setup( void ) ;\nextern void loop( void ) ;\n\n\n//#define NOT_A_PIN 0 // defined in pio.h/EPioType\n#define NOT_A_PORT 0\n\n#define NOT_AN_INTERRUPT -1\n\n\ntypedef void (*voidFuncPtr)( void ) ;\n\n/* Define attribute */\n#if defined ( __CC_ARM ) /* Keil uVision 4 */\n #define WEAK (__attribute__ ((weak)))\n#elif defined ( __ICCARM__ ) /* IAR Ewarm 5.41+ */\n #define WEAK __weak\n#elif defined ( __GNUC__ ) /* GCC CS */\n #define WEAK __attribute__ ((weak))\n#endif\n\n\n\n#ifdef __cplusplus\n} // extern \"C\"\n\n#include \"WCharacter.h\"\n#include \"WString.h\"\n#include \"Tone.h\"\n#include \"WMath.h\"\n#include \"HardwareSerial.h\"\n#include \"wiring_pulse.h\"\n\n#include \"variant.h\"\n\nvoid tone(uint8_t _pin, unsigned int frequency, unsigned long duration = 0);\nvoid noTone(uint8_t _pin);\n\n#endif // __cplusplus\n\n\n#include \"wiring.h\"\n#include \"wiring_digital.h\"\n#include \"wiring_analog.h\"\n#include \"wiring_shift.h\"\n#include \"WInterrupts.h\"\n#include \"digitalWriteFast.h\"\n#endif // Arduino_h\n"

},

{

"path": "arduino/opencr_arduino/opencr/cores/arduino/Client.h",

"content": "/*\n Client.h - Base class that provides Client\n Copyright (c) 2011 Adrian McEwen. All right reserved.\n\n This library is free software; you can redistribute it and/or\n modify it under the terms of the GNU Lesser General Public\n License as published by the Free Software Foundation; either\n version 2.1 of the License, or (at your option) any later version.\n\n This library is distributed in the hope that it will be useful,\n but WITHOUT ANY WARRANTY; without even the implied warranty of\n MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU\n Lesser General Public License for more details.\n\n You should have received a copy of the GNU Lesser General Public\n License along with this library; if not, write to the Free Software\n Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA\n*/\n\n#ifndef client_h\n#define client_h\n#include \"Print.h\"\n#include \"Stream.h\"\n#include \"IPAddress.h\"\n\nclass Client : public Stream {\n\npublic:\n virtual int connect(IPAddress ip, uint16_t port) =0;\n virtual int connect(const char *host, uint16_t port) =0;\n virtual size_t write(uint8_t) =0;\n virtual size_t write(const uint8_t *buf, size_t size) =0;\n virtual int available() = 0;\n virtual int read() = 0;\n virtual int read(uint8_t *buf, size_t size) = 0;\n virtual int peek() = 0;\n virtual void flush() = 0;\n virtual void stop() = 0;\n virtual uint8_t connected() = 0;\n virtual operator bool() = 0;\nprotected:\n uint8_t* rawIPAddress(IPAddress& addr) { return addr.raw_address(); };\n};\n\n#endif\n"

},

{

"path": "arduino/opencr_arduino/opencr/cores/arduino/HardwareSerial.h",

"content": "/*\n Copyright (c) 2011 Arduino. All right reserved.\n\n This library is free software; you can redistribute it and/or\n modify it under the terms of the GNU Lesser General Public\n License as published by the Free Software Foundation; either\n version 2.1 of the License, or (at your option) any later version.\n\n This library is distributed in the hope that it will be useful,\n but WITHOUT ANY WARRANTY; without even the implied warranty of\n MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. \n See the GNU Lesser General Public License for more details.\n\n You should have received a copy of the GNU Lesser General Public\n License along with this library; if not, write to the Free Software\n Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA\n*/\n\n#ifndef HardwareSerial_h\n#define HardwareSerial_h\n\n#include \n\n#include \"Stream.h\"\n\nclass HardwareSerial : public Stream\n{\n public:\n virtual void begin(unsigned long) = 0;\n virtual void end() = 0;\n virtual int available(void) = 0;\n virtual int peek(void) = 0;\n virtual int read(void) = 0;\n virtual void flush(void) = 0;\n virtual size_t write(uint8_t) = 0;\n using Print::write; // pull in write(str) and write(buf, size) from Print\n virtual operator bool() = 0;\n};\n\nextern void serialEventRun(void) __attribute__((weak));\n\n#endif\n"

},

{

"path": "arduino/opencr_arduino/opencr/cores/arduino/HardwareTimer.cpp",

"content": "/******************************************************************************\n * The MIT License\n *\n * Copyright (c) 2010 Bryan Newbold.\n *\n * Permission is hereby granted, free of charge, to any person\n * obtaining a copy of this software and associated documentation\n * files (the \"Software\"), to deal in the Software without\n * restriction, including without limitation the rights to use, copy,\n * modify, merge, publish, distribute, sublicense, and/or sell copies\n * of the Software, and to permit persons to whom the Software is\n * furnished to do so, subject to the following conditions:\n *\n * The above copyright notice and this permission notice shall be\n * included in all copies or substantial portions of the Software.\n *\n * THE SOFTWARE IS PROVIDED \"AS IS\", WITHOUT WARRANTY OF ANY KIND,\n * EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF\n * MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND\n * NONINFRINGEMENT. IN NO EVENT SHALL THE AUTHORS OR COPYRIGHT HOLDERS\n * BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY, WHETHER IN AN\n * ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, OUT OF OR IN\n * CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE\n * SOFTWARE.\n *****************************************************************************/\n\n#include \n\n#include \n#include \"drv_timer.h\"\n#include \"variant.h\"\n#include \"HardwareTimer.h\"\n\n\n#define MAX_RELOAD ((1 << 16) - 1)\n\nHardwareTimer::HardwareTimer(uint8_t timerNum) {\n if (timerNum > TIMER_CH_MAX) {\n tim_num = 0;\n }\n\n tim_num = timerNum;\n}\n\nvoid HardwareTimer::pause(void) {\n drv_timer_pause(tim_num);\n}\n\nvoid HardwareTimer::resume(void) {\n drv_timer_resume(tim_num);\n}\n\nvoid HardwareTimer::stop(void) {\n drv_timer_pause(tim_num);\n}\n\nvoid HardwareTimer::start(void) {\n drv_timer_resume(tim_num);\n}\n\nuint16_t HardwareTimer::setPeriod(uint32_t microseconds) {\n\n drv_timer_set_period(tim_num, microseconds);\n\n return 0;\n}\n\nvoid HardwareTimer::attachInterrupt(voidFuncPtr handler) {\n drv_timer_attachInterrupt(tim_num, handler);\n}\n\nvoid HardwareTimer::detachInterrupt(void) {\n drv_timer_detachInterrupt(tim_num);\n}\n\nvoid HardwareTimer::refresh(void) {\n drv_timer_refresh(tim_num);\n}\n"

},

{

"path": "arduino/opencr_arduino/opencr/cores/arduino/HardwareTimer.h",

"content": "/******************************************************************************\n * The MIT License\n *\n * Copyright (c) 2010 Bryan Newbold.\n *\n * Permission is hereby granted, free of charge, to any person\n * obtaining a copy of this software and associated documentation\n * files (the \"Software\"), to deal in the Software without\n * restriction, including without limitation the rights to use, copy,\n * modify, merge, publish, distribute, sublicense, and/or sell copies\n * of the Software, and to permit persons to whom the Software is\n * furnished to do so, subject to the following conditions:\n *\n * The above copyright notice and this permission notice shall be\n * included in all copies or substantial portions of the Software.\n *\n * THE SOFTWARE IS PROVIDED \"AS IS\", WITHOUT WARRANTY OF ANY KIND,\n * EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF\n * MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND\n * NONINFRINGEMENT. IN NO EVENT SHALL THE AUTHORS OR COPYRIGHT HOLDERS\n * BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY, WHETHER IN AN\n * ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, OUT OF OR IN\n * CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE\n * SOFTWARE.\n *****************************************************************************/\n\n\n#ifndef _HARDWARETIMER_H_\n#define _HARDWARETIMER_H_\n\n#include \n\n\n\n\n\nclass HardwareTimer {\nprivate:\n uint8_t tim_num;\npublic:\n HardwareTimer(uint8_t timerNum);\n\n void pause(void);\n void resume(void);\n void stop(void);\n void start(void);\n uint16_t setPeriod(uint32_t microseconds);\n void attachInterrupt(voidFuncPtr handler);\n void detachInterrupt(void);\n void refresh(void);\n};\n\n#endif\n"

},

{

"path": "arduino/opencr_arduino/opencr/cores/arduino/IPAddress.cpp",

"content": "/*\n IPAddress.cpp - Base class that provides IPAddress\n Copyright (c) 2011 Adrian McEwen. All right reserved.\n\n This library is free software; you can redistribute it and/or\n modify it under the terms of the GNU Lesser General Public\n License as published by the Free Software Foundation; either\n version 2.1 of the License, or (at your option) any later version.\n\n This library is distributed in the hope that it will be useful,\n but WITHOUT ANY WARRANTY; without even the implied warranty of\n MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU\n Lesser General Public License for more details.\n\n You should have received a copy of the GNU Lesser General Public\n License along with this library; if not, write to the Free Software\n Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA\n*/\n\n#include \n#include \n\nIPAddress::IPAddress()\n{\n _address.dword = 0;\n}\n\nIPAddress::IPAddress(uint8_t first_octet, uint8_t second_octet, uint8_t third_octet, uint8_t fourth_octet)\n{\n _address.bytes[0] = first_octet;\n _address.bytes[1] = second_octet;\n _address.bytes[2] = third_octet;\n _address.bytes[3] = fourth_octet;\n}\n\nIPAddress::IPAddress(uint32_t address)\n{\n _address.dword = address;\n}\n\nIPAddress::IPAddress(const uint8_t *address)\n{\n memcpy(_address.bytes, address, sizeof(_address.bytes));\n}\n\nbool IPAddress::fromString(const char *address)\n{\n uint16_t acc = 0; // Accumulator\n uint8_t dots = 0;\n\n while (*address)\n {\n char c = *address++;\n if (c >= '0' && c <= '9')\n {\n acc = acc * 10 + (c - '0');\n if (acc > 255) {\n // Value out of [0..255] range\n return false;\n }\n }\n else if (c == '.')\n {\n if (dots == 3) {\n // Too much dots (there must be 3 dots)\n return false;\n }\n _address.bytes[dots++] = acc;\n acc = 0;\n }\n else\n {\n // Invalid char\n return false;\n }\n }\n\n if (dots != 3) {\n // Too few dots (there must be 3 dots)\n return false;\n }\n _address.bytes[3] = acc;\n return true;\n}\n\nIPAddress& IPAddress::operator=(const uint8_t *address)\n{\n memcpy(_address.bytes, address, sizeof(_address.bytes));\n return *this;\n}\n\nIPAddress& IPAddress::operator=(uint32_t address)\n{\n _address.dword = address;\n return *this;\n}\n\nbool IPAddress::operator==(const uint8_t* addr) const\n{\n return memcmp(addr, _address.bytes, sizeof(_address.bytes)) == 0;\n}\n\nsize_t IPAddress::printTo(Print& p) const\n{\n size_t n = 0;\n for (int i =0; i < 3; i++)\n {\n n += p.print(_address.bytes[i], DEC);\n n += p.print('.');\n }\n n += p.print(_address.bytes[3], DEC);\n return n;\n}\n\n"

},

{

"path": "arduino/opencr_arduino/opencr/cores/arduino/IPAddress.h",

"content": "/*\n IPAddress.h - Base class that provides IPAddress\n Copyright (c) 2011 Adrian McEwen. All right reserved.\n\n This library is free software; you can redistribute it and/or\n modify it under the terms of the GNU Lesser General Public\n License as published by the Free Software Foundation; either\n version 2.1 of the License, or (at your option) any later version.\n\n This library is distributed in the hope that it will be useful,\n but WITHOUT ANY WARRANTY; without even the implied warranty of\n MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU\n Lesser General Public License for more details.\n\n You should have received a copy of the GNU Lesser General Public\n License along with this library; if not, write to the Free Software\n Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA\n*/\n\n#ifndef IPAddress_h\n#define IPAddress_h\n\n#include \n#include \"Printable.h\"\n#include \"WString.h\"\n\n// A class to make it easier to handle and pass around IP addresses\n\nclass IPAddress : public Printable {\nprivate:\n union {\n\tuint8_t bytes[4]; // IPv4 address\n\tuint32_t dword;\n } _address;\n\n // Access the raw byte array containing the address. Because this returns a pointer\n // to the internal structure rather than a copy of the address this function should only\n // be used when you know that the usage of the returned uint8_t* will be transient and not\n // stored.\n uint8_t* raw_address() { return _address.bytes; };\n\npublic:\n // Constructors\n IPAddress();\n IPAddress(uint8_t first_octet, uint8_t second_octet, uint8_t third_octet, uint8_t fourth_octet);\n IPAddress(uint32_t address);\n IPAddress(const uint8_t *address);\n\n bool fromString(const char *address);\n bool fromString(const String &address) { return fromString(address.c_str()); }\n\n // Overloaded cast operator to allow IPAddress objects to be used where a pointer\n // to a four-byte uint8_t array is expected\n operator uint32_t() const { return _address.dword; };\n bool operator==(const IPAddress& addr) const { return _address.dword == addr._address.dword; };\n bool operator==(const uint8_t* addr) const;\n\n // Overloaded index operator to allow getting and setting individual octets of the address\n uint8_t operator[](int index) const { return _address.bytes[index]; };\n uint8_t& operator[](int index) { return _address.bytes[index]; };\n\n // Overloaded copy operators to allow initialisation of IPAddress objects from other types\n IPAddress& operator=(const uint8_t *address);\n IPAddress& operator=(uint32_t address);\n\n virtual size_t printTo(Print& p) const;\n\n friend class EthernetClass;\n friend class UDP;\n friend class Client;\n friend class Server;\n friend class DhcpClass;\n friend class DNSClient;\n};\n\nconst IPAddress INADDR_NONE(0,0,0,0);\n\n#endif\n"

},

{

"path": "arduino/opencr_arduino/opencr/cores/arduino/Print.cpp",

"content": "/*\r\n Print.cpp - Base class that provides print() and println()\r\n Copyright (c) 2008 David A. Mellis. All right reserved.\r\n\r\n This library is free software; you can redistribute it and/or\r\n modify it under the terms of the GNU Lesser General Public\r\n License as published by the Free Software Foundation; either\r\n version 2.1 of the License, or (at your option) any later version.\r\n\r\n This library is distributed in the hope that it will be useful,\r\n but WITHOUT ANY WARRANTY; without even the implied warranty of\r\n MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU\r\n Lesser General Public License for more details.\r\n\r\n You should have received a copy of the GNU Lesser General Public\r\n License along with this library; if not, write to the Free Software\r\n Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA\r\n\r\n Modified 23 November 2006 by David A. Mellis\r\n */\r\n\r\n#include \r\n#include \r\n#include \r\n#include \r\n#include \r\n#include \"Arduino.h\"\r\n\r\n#include \"Print.h\"\r\n\r\n// Public Methods //////////////////////////////////////////////////////////////\r\n\r\n/* default implementation: may be overridden */\r\nsize_t Print::write(const uint8_t *buffer, size_t size)\r\n{\r\n size_t n = 0;\r\n while (size--) {\r\n n += write(*buffer++);\r\n }\r\n return n;\r\n}\r\n\r\nsize_t Print::print(const __FlashStringHelper *ifsh)\r\n{\r\n return print(reinterpret_cast(ifsh));\r\n}\r\n\r\nsize_t Print::print(const String &s)\r\n{\r\n return write(s.c_str(), s.length());\r\n}\r\n\r\nsize_t Print::print(const char str[])\r\n{\r\n return write(str);\r\n}\r\n\r\nsize_t Print::print(char c)\r\n{\r\n return write(c);\r\n}\r\n\r\nsize_t Print::print(unsigned char b, int base)\r\n{\r\n return print((unsigned long) b, base);\r\n}\r\n\r\nsize_t Print::print(int n, int base)\r\n{\r\n return print((long) n, base);\r\n}\r\n\r\nsize_t Print::print(unsigned int n, int base)\r\n{\r\n return print((unsigned long) n, base);\r\n}\r\n\r\nsize_t Print::print(long n, int base)\r\n{\r\n if (base == 0) {\r\n return write(n);\r\n } else if (base == 10) {\r\n if (n < 0) {\r\n int t = print('-');\r\n n = -n;\r\n return printNumber(n, 10) + t;\r\n }\r\n return printNumber(n, 10);\r\n } else {\r\n return printNumber(n, base);\r\n }\r\n}\r\n\r\nsize_t Print::print(unsigned long n, int base)\r\n{\r\n if (base == 0) return write(n);\r\n else return printNumber(n, base);\r\n}\r\n\r\nsize_t Print::print(double n, int digits)\r\n{\r\n return printFloat(n, digits);\r\n}\r\n\r\nsize_t Print::println(const __FlashStringHelper *ifsh)\r\n{\r\n size_t n = print(ifsh);\r\n n += println();\r\n return n;\r\n}\r\n\r\nsize_t Print::print(const Printable& x)\r\n{\r\n return x.printTo(*this);\r\n}\r\n\r\nsize_t Print::println(void)\r\n{\r\n size_t n = print('\\r');\r\n n += print('\\n');\r\n return n;\r\n}\r\n\r\nsize_t Print::println(const String &s)\r\n{\r\n size_t n = print(s);\r\n n += println();\r\n return n;\r\n}\r\n\r\nsize_t Print::println(const char c[])\r\n{\r\n size_t n = print(c);\r\n n += println();\r\n return n;\r\n}\r\n\r\nsize_t Print::println(char c)\r\n{\r\n size_t n = print(c);\r\n n += println();\r\n return n;\r\n}\r\n\r\nsize_t Print::println(unsigned char b, int base)\r\n{\r\n size_t n = print(b, base);\r\n n += println();\r\n return n;\r\n}\r\n\r\nsize_t Print::println(int num, int base)\r\n{\r\n size_t n = print(num, base);\r\n n += println();\r\n return n;\r\n}\r\n\r\nsize_t Print::println(unsigned int num, int base)\r\n{\r\n size_t n = print(num, base);\r\n n += println();\r\n return n;\r\n}\r\n\r\nsize_t Print::println(long num, int base)\r\n{\r\n size_t n = print(num, base);\r\n n += println();\r\n return n;\r\n}\r\n\r\nsize_t Print::println(unsigned long num, int base)\r\n{\r\n size_t n = print(num, base);\r\n n += println();\r\n return n;\r\n}\r\n\r\nsize_t Print::println(double num, int digits)\r\n{\r\n size_t n = print(num, digits);\r\n n += println();\r\n return n;\r\n}\r\n\r\nsize_t Print::println(const Printable& x)\r\n{\r\n size_t n = print(x);\r\n n += println();\r\n return n;\r\n}\r\n\r\nsize_t Print::printf(const char *fmt, ... )\r\n{\r\n char buf[256]; // resulting string limited to 128 chars\r\n char buf_out[256];\r\n va_list args;\r\n size_t i;\r\n int i_out;\r\n\r\n\r\n va_start (args, fmt );\r\n vsnprintf(buf, 256, fmt, args);\r\n va_end (args);\r\n\r\n i_out = 0;\r\n for( i=0; i 4294967040.0) return print (\"ovf\"); // constant determined empirically\r\n if (number <-4294967040.0) return print (\"ovf\"); // constant determined empirically\r\n\r\n // Handle negative numbers\r\n if (number < 0.0)\r\n {\r\n n += print('-');\r\n number = -number;\r\n }\r\n\r\n // Round correctly so that print(1.999, 2) prints as \"2.00\"\r\n double rounding = 0.5;\r\n for (uint8_t i=0; i 0) {\r\n n += print(\".\");\r\n }\r\n\r\n // Extract digits from the remainder one at a time\r\n while (digits-- > 0)\r\n {\r\n remainder *= 10.0;\r\n int toPrint = int(remainder);\r\n n += print(toPrint);\r\n remainder -= toPrint;\r\n }\r\n\r\n return n;\r\n}\r\n"

},

{

"path": "arduino/opencr_arduino/opencr/cores/arduino/Print.h",

"content": "/*\n Print.h - Base class that provides print() and println()\n Copyright (c) 2008 David A. Mellis. All right reserved.\n\n This library is free software; you can redistribute it and/or\n modify it under the terms of the GNU Lesser General Public\n License as published by the Free Software Foundation; either\n version 2.1 of the License, or (at your option) any later version.\n\n This library is distributed in the hope that it will be useful,\n but WITHOUT ANY WARRANTY; without even the implied warranty of\n MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU\n Lesser General Public License for more details.\n\n You should have received a copy of the GNU Lesser General Public\n License along with this library; if not, write to the Free Software\n Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA\n*/\n\n#ifndef Print_h\n#define Print_h\n\n#include \n#include // for size_t\n#include \n\n#include \"WString.h\"\n#include \"Printable.h\"\n\n#define DEC 10\n#define HEX 16\n#define OCT 8\n#define BIN 2\n\nclass Print\n{\n private:\n int write_error;\n size_t printNumber(unsigned long, uint8_t);\n size_t printFloat(double, uint8_t);\n protected:\n void setWriteError(int err = 1) { write_error = err; }\n public:\n Print() : write_error(0) {}\n\n int getWriteError() { return write_error; }\n void clearWriteError() { setWriteError(0); }\n\n virtual size_t write(uint8_t) = 0;\n size_t write(const char *str) {\n if (str == NULL) return 0;\n return write((const uint8_t *)str, strlen(str));\n }\n virtual size_t write(const uint8_t *buffer, size_t size);\n size_t write(const char *buffer, size_t size) {\n return write((const uint8_t *)buffer, size);\n }\n\n size_t print(const __FlashStringHelper *);\n size_t print(const String &);\n size_t print(const char[]);\n size_t print(char);\n size_t print(unsigned char, int = DEC);\n size_t print(int, int = DEC);\n size_t print(unsigned int, int = DEC);\n size_t print(long, int = DEC);\n size_t print(unsigned long, int = DEC);\n size_t print(double, int = 2);\n size_t print(const Printable&);\n\n size_t println(const __FlashStringHelper *);\n size_t println(const String &s);\n size_t println(const char[]);\n size_t println(char);\n size_t println(unsigned char, int = DEC);\n size_t println(int, int = DEC);\n size_t println(unsigned int, int = DEC);\n size_t println(long, int = DEC);\n size_t println(unsigned long, int = DEC);\n size_t println(double, int = 2);\n size_t println(const Printable&);\n size_t println(void);\n\n size_t printf(const char *fmt, ... );\n\n};\n\n#endif\n"

},

{

"path": "arduino/opencr_arduino/opencr/cores/arduino/Printable.h",

"content": "/*\n Printable.h - Interface class that allows printing of complex types\n Copyright (c) 2011 Adrian McEwen. All right reserved.\n\n This library is free software; you can redistribute it and/or\n modify it under the terms of the GNU Lesser General Public\n License as published by the Free Software Foundation; either\n version 2.1 of the License, or (at your option) any later version.\n\n This library is distributed in the hope that it will be useful,\n but WITHOUT ANY WARRANTY; without even the implied warranty of\n MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU\n Lesser General Public License for more details.\n\n You should have received a copy of the GNU Lesser General Public\n License along with this library; if not, write to the Free Software\n Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA\n*/\n\n#ifndef Printable_h\n#define Printable_h\n\n#include \n\nclass Print;\n\n/** The Printable class provides a way for new classes to allow themselves to be printed.\n By deriving from Printable and implementing the printTo method, it will then be possible\n for users to print out instances of this class by passing them into the usual\n Print::print and Print::println methods.\n*/\n\nclass Printable\n{\n public:\n virtual size_t printTo(Print& p) const = 0;\n};\n\n#endif\n\n"

},

{

"path": "arduino/opencr_arduino/opencr/cores/arduino/Reset.h",

"content": "/*\n Copyright (c) 2012 Arduino. All right reserved.\n\n This library is free software; you can redistribute it and/or\n modify it under the terms of the GNU Lesser General Public\n License as published by the Free Software Foundation; either\n version 2.1 of the License, or (at your option) any later version.\n\n This library is distributed in the hope that it will be useful,\n but WITHOUT ANY WARRANTY; without even the implied warranty of\n MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE.\n See the GNU Lesser General Public License for more details.\n\n You should have received a copy of the GNU Lesser General Public\n License along with this library; if not, write to the Free Software\n Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA\n*/\n\n#ifndef RESET_H\n#define RESET_H\n\n#ifdef __cplusplus\nextern \"C\" {\n#endif\n\nvoid initiateReset(int ms);\nvoid tickReset();\nvoid cancelReset();\n\n#ifdef __cplusplus\n}\n#endif\n\n#endif\n"

},

{

"path": "arduino/opencr_arduino/opencr/cores/arduino/RingBuffer.cpp",

"content": "/*\r\n Copyright (c) 2011 Arduino. All right reserved.\r\n\r\n This library is free software; you can redistribute it and/or\r\n modify it under the terms of the GNU Lesser General Public\r\n License as published by the Free Software Foundation; either\r\n version 2.1 of the License, or (at your option) any later version.\r\n\r\n This library is distributed in the hope that it will be useful,\r\n but WITHOUT ANY WARRANTY; without even the implied warranty of\r\n MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. \r\n See the GNU Lesser General Public License for more details.\r\n\r\n You should have received a copy of the GNU Lesser General Public\r\n License along with this library; if not, write to the Free Software\r\n Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA\r\n*/\r\n\r\n#include \"RingBuffer.h\"\r\n#include \r\n\r\nRingBuffer::RingBuffer( void )\r\n{\r\n memset( (void *)_aucBuffer, 0, RING_BUFFER_SIZE ) ;\r\n _iHead=0 ;\r\n _iTail=0 ;\r\n}\r\n\r\nvoid RingBuffer::store_char( uint8_t c )\r\n{\r\n int i = (uint32_t)(_iHead + 1) % RING_BUFFER_SIZE ;\r\n\r\n // if we should be storing the received character into the location\r\n // just before the tail (meaning that the head would advance to the\r\n // current location of the tail), we're about to overflow the buffer\r\n // and so we don't write the character or advance the head.\r\n if ( i != _iTail )\r\n {\r\n _aucBuffer[_iHead] = c ;\r\n _iHead = i ;\r\n }\r\n}\r\n\r\n"

},

{

"path": "arduino/opencr_arduino/opencr/cores/arduino/RingBuffer.h",

"content": "/*\r\n Copyright (c) 2011 Arduino. All right reserved.\r\n\r\n This library is free software; you can redistribute it and/or\r\n modify it under the terms of the GNU Lesser General Public\r\n License as published by the Free Software Foundation; either\r\n version 2.1 of the License, or (at your option) any later version.\r\n\r\n This library is distributed in the hope that it will be useful,\r\n but WITHOUT ANY WARRANTY; without even the implied warranty of\r\n MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. \r\n See the GNU Lesser General Public License for more details.\r\n\r\n You should have received a copy of the GNU Lesser General Public\r\n License along with this library; if not, write to the Free Software\r\n Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA\r\n*/\r\n\r\n#ifndef _RING_BUFFER_\r\n#define _RING_BUFFER_\r\n\r\n#include \r\n\r\n// Define constants and variables for buffering incoming serial data. We're\r\n// using a ring buffer (I think), in which head is the index of the location\r\n// to which to write the next incoming character and tail is the index of the\r\n// location from which to read.\r\n#define RING_BUFFER_SIZE 128\r\n\r\nclass RingBuffer\r\n{\r\n public:\r\n volatile uint8_t _aucBuffer[RING_BUFFER_SIZE] ;\r\n volatile int _iHead ;\r\n volatile int _iTail ;\r\n\r\n public:\r\n RingBuffer( void ) ;\r\n void store_char( uint8_t c ) ;\r\n} ;\r\n\r\n#endif /* _RING_BUFFER_ */\r\n"

},

{

"path": "arduino/opencr_arduino/opencr/cores/arduino/Server.h",

"content": "/*\n Server.h - Base class that provides Server\n Copyright (c) 2011 Adrian McEwen. All right reserved.\n\n This library is free software; you can redistribute it and/or\n modify it under the terms of the GNU Lesser General Public\n License as published by the Free Software Foundation; either\n version 2.1 of the License, or (at your option) any later version.\n\n This library is distributed in the hope that it will be useful,\n but WITHOUT ANY WARRANTY; without even the implied warranty of\n MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU\n Lesser General Public License for more details.\n\n You should have received a copy of the GNU Lesser General Public\n License along with this library; if not, write to the Free Software\n Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA\n*/\n\n#ifndef server_h\n#define server_h\n\n#include \"Print.h\"\n\nclass Server : public Print {\npublic:\n virtual void begin() =0;\n};\n\n#endif\n"

},

{

"path": "arduino/opencr_arduino/opencr/cores/arduino/Stream.cpp",

"content": "/*\r\n Stream.cpp - adds parsing methods to Stream class\r\n Copyright (c) 2008 David A. Mellis. All right reserved.\r\n\r\n This library is free software; you can redistribute it and/or\r\n modify it under the terms of the GNU Lesser General Public\r\n License as published by the Free Software Foundation; either\r\n version 2.1 of the License, or (at your option) any later version.\r\n\r\n This library is distributed in the hope that it will be useful,\r\n but WITHOUT ANY WARRANTY; without even the implied warranty of\r\n MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU\r\n Lesser General Public License for more details.\r\n\r\n You should have received a copy of the GNU Lesser General Public\r\n License along with this library; if not, write to the Free Software\r\n Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA\r\n\r\n Created July 2011\r\n parsing functions based on TextFinder library by Michael Margolis\r\n\r\n findMulti/findUntil routines written by Jim Leonard/Xuth\r\n */\r\n\r\n#include \"Arduino.h\"\r\n#include \"Stream.h\"\r\n\r\n#define PARSE_TIMEOUT 1000 // default number of milli-seconds to wait\r\n#define NO_SKIP_CHAR 1 // a magic char not found in a valid ASCII numeric field\r\n\r\n// private method to read stream with timeout\r\nint Stream::timedRead()\r\n{\r\n int c;\r\n _startMillis = millis();\r\n do {\r\n c = read();\r\n if (c >= 0) return c;\r\n } while(millis() - _startMillis < _timeout);\r\n return -1; // -1 indicates timeout\r\n}\r\n\r\n// private method to peek stream with timeout\r\nint Stream::timedPeek()\r\n{\r\n int c;\r\n _startMillis = millis();\r\n do {\r\n c = peek();\r\n if (c >= 0) return c;\r\n } while(millis() - _startMillis < _timeout);\r\n return -1; // -1 indicates timeout\r\n}\r\n\r\n// returns peek of the next digit in the stream or -1 if timeout\r\n// discards non-numeric characters\r\nint Stream::peekNextDigit()\r\n{\r\n int c;\r\n while (1) {\r\n c = timedPeek();\r\n if (c < 0) return c; // timeout\r\n if (c == '-') return c;\r\n if (c >= '0' && c <= '9') return c;\r\n read(); // discard non-numeric\r\n }\r\n}\r\n\r\n// Public Methods\r\n//////////////////////////////////////////////////////////////\r\n\r\nvoid Stream::setTimeout(unsigned long timeout) // sets the maximum number of milliseconds to wait\r\n{\r\n _timeout = timeout;\r\n}\r\n\r\n // find returns true if the target string is found\r\nbool Stream::find(char *target)\r\n{\r\n return findUntil(target, strlen(target), NULL, 0);\r\n}\r\n\r\n// reads data from the stream until the target string of given length is found\r\n// returns true if target string is found, false if timed out\r\nbool Stream::find(char *target, size_t length)\r\n{\r\n return findUntil(target, length, NULL, 0);\r\n}\r\n\r\n// as find but search ends if the terminator string is found\r\nbool Stream::findUntil(char *target, char *terminator)\r\n{\r\n return findUntil(target, strlen(target), terminator, strlen(terminator));\r\n}\r\n\r\n// reads data from the stream until the target string of the given length is found\r\n// search terminated if the terminator string is found\r\n// returns true if target string is found, false if terminated or timed out\r\nbool Stream::findUntil(char *target, size_t targetLen, char *terminator, size_t termLen)\r\n{\r\n if (terminator == NULL) {\r\n MultiTarget t[1] = {{target, targetLen, 0}};\r\n return findMulti(t, 1) == 0 ? true : false;\r\n } else {\r\n MultiTarget t[2] = {{target, targetLen, 0}, {terminator, termLen, 0}};\r\n return findMulti(t, 2) == 0 ? true : false;\r\n }\r\n}\r\n\r\n\r\n// returns the first valid (long) integer value from the current position.\r\n// initial characters that are not digits (or the minus sign) are skipped\r\n// function is terminated by the first character that is not a digit.\r\nlong Stream::parseInt()\r\n{\r\n return parseInt(NO_SKIP_CHAR); // terminate on first non-digit character (or timeout)\r\n}\r\n\r\n// as above but a given skipChar is ignored\r\n// this allows format characters (typically commas) in values to be ignored\r\nlong Stream::parseInt(char skipChar)\r\n{\r\n bool isNegative = false;\r\n long value = 0;\r\n int c;\r\n\r\n c = peekNextDigit();\r\n // ignore non numeric leading characters\r\n if(c < 0)\r\n return 0; // zero returned if timeout\r\n\r\n do{\r\n if(c == skipChar)\r\n ; // ignore this charactor\r\n else if(c == '-')\r\n isNegative = true;\r\n else if(c >= '0' && c <= '9') // is c a digit?\r\n value = value * 10 + c - '0';\r\n read(); // consume the character we got with peek\r\n c = timedPeek();\r\n }\r\n while( (c >= '0' && c <= '9') || c == skipChar );\r\n\r\n if(isNegative)\r\n value = -value;\r\n return value;\r\n}\r\n\r\n\r\n// as parseInt but returns a floating point value\r\nfloat Stream::parseFloat()\r\n{\r\n return parseFloat(NO_SKIP_CHAR);\r\n}\r\n\r\n// as above but the given skipChar is ignored\r\n// this allows format characters (typically commas) in values to be ignored\r\nfloat Stream::parseFloat(char skipChar){\r\n bool isNegative = false;\r\n bool isFraction = false;\r\n long value = 0;\r\n int c;//char c;\r\n float fraction = 1.0;\r\n\r\n c = peekNextDigit();\r\n // ignore non numeric leading characters\r\n if(c < 0)\r\n return 0; // zero returned if timeout\r\n\r\n do{\r\n if(c == skipChar)\r\n ; // ignore\r\n else if(c == '-')\r\n isNegative = true;\r\n else if (c == '.')\r\n isFraction = true;\r\n else if(c >= '0' && c <= '9') { // is c a digit?\r\n value = value * 10 + c - '0';\r\n if(isFraction)\r\n fraction *= 0.1;\r\n }\r\n read(); // consume the character we got with peek\r\n c = timedPeek();\r\n }\r\n while( (c >= '0' && c <= '9') || c == '.' || c == skipChar );\r\n\r\n if(isNegative)\r\n value = -value;\r\n if(isFraction)\r\n return value * fraction;\r\n else\r\n return value;\r\n}\r\n\r\n// read characters from stream into buffer\r\n// terminates if length characters have been read, or timeout (see setTimeout)\r\n// returns the number of characters placed in the buffer\r\n// the buffer is NOT null terminated.\r\n//\r\nsize_t Stream::readBytes(char *buffer, size_t length)\r\n{\r\n size_t count = 0;\r\n while (count < length) {\r\n int c = timedRead();\r\n if (c < 0) break;\r\n *buffer++ = (char)c;\r\n count++;\r\n }\r\n return count;\r\n}\r\n\r\n\r\n// as readBytes with terminator character\r\n// terminates if length characters have been read, timeout, or if the terminator character detected\r\n// returns the number of characters placed in the buffer (0 means no valid data found)\r\n\r\nsize_t Stream::readBytesUntil(char terminator, char *buffer, size_t length)\r\n{\r\n if (length < 1) return 0;\r\n size_t index = 0;\r\n while (index < length) {\r\n int c = timedRead();\r\n if (c < 0 || c == terminator) break;\r\n *buffer++ = (char)c;\r\n index++;\r\n }\r\n return index; // return number of characters, not including null terminator\r\n}\r\n\r\nString Stream::readString()\r\n{\r\n String ret;\r\n int c = timedRead();\r\n while (c >= 0)\r\n {\r\n ret += (char)c;\r\n c = timedRead();\r\n }\r\n return ret;\r\n}\r\n\r\nString Stream::readStringUntil(char terminator)\r\n{\r\n String ret;\r\n int c = timedRead();\r\n while (c >= 0 && c != terminator)\r\n {\r\n ret += (char)c;\r\n c = timedRead();\r\n }\r\n return ret;\r\n}\r\n\r\nint Stream::findMulti( struct Stream::MultiTarget *targets, int tCount) {\r\n // any zero length target string automatically matches and would make\r\n // a mess of the rest of the algorithm.\r\n for (struct MultiTarget *t = targets; t < targets+tCount; ++t) {\r\n if (t->len <= 0)\r\n return t - targets;\r\n }\r\n\r\n while (1) {\r\n int c = timedRead();\r\n if (c < 0)\r\n return -1;\r\n\r\n for (struct MultiTarget *t = targets; t < targets+tCount; ++t) {\r\n // the simple case is if we match, deal with that first.\r\n if (c == t->str[t->index]) {\r\n if (++t->index == t->len)\r\n return t - targets;\r\n else\r\n continue;\r\n }\r\n\r\n // if not we need to walk back and see if we could have matched further\r\n // down the stream (ie '1112' doesn't match the first position in '11112'\r\n // but it will match the second position so we can't just reset the current\r\n // index to 0 when we find a mismatch.\r\n if (t->index == 0)\r\n continue;\r\n\r\n int origIndex = t->index;\r\n do {\r\n --t->index;\r\n // first check if current char works against the new current index\r\n if (c != t->str[t->index])\r\n continue;\r\n\r\n // if it's the only char then we're good, nothing more to check\r\n if (t->index == 0) {\r\n t->index++;\r\n break;\r\n }\r\n\r\n // otherwise we need to check the rest of the found string\r\n int diff = origIndex - t->index;\r\n size_t i;\r\n for (i = 0; i < t->index; ++i) {\r\n if (t->str[i] != t->str[i + diff])\r\n break;\r\n }\r\n\r\n // if we successfully got through the previous loop then our current\r\n // index is good.\r\n if (i == t->index) {\r\n t->index++;\r\n break;\r\n }\r\n\r\n // otherwise we just try the next index\r\n } while (t->index);\r\n }\r\n }\r\n // unreachable\r\n return -1;\r\n}\r\n"

},

{

"path": "arduino/opencr_arduino/opencr/cores/arduino/Stream.h",

"content": "/*\n Stream.h - base class for character-based streams.\n Copyright (c) 2010 David A. Mellis. All right reserved.\n\n This library is free software; you can redistribute it and/or\n modify it under the terms of the GNU Lesser General Public\n License as published by the Free Software Foundation; either\n version 2.1 of the License, or (at your option) any later version.\n\n This library is distributed in the hope that it will be useful,\n but WITHOUT ANY WARRANTY; without even the implied warranty of\n MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU\n Lesser General Public License for more details.\n\n You should have received a copy of the GNU Lesser General Public\n License along with this library; if not, write to the Free Software\n Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA\n\n parsing functions based on TextFinder library by Michael Margolis\n*/\n\n#ifndef Stream_h\n#define Stream_h\n\n#include \n#include \"Print.h\"\n\n// compatability macros for testing\n/*\n#define getInt() parseInt()\n#define getInt(skipChar) parseInt(skipchar)\n#define getFloat() parseFloat()\n#define getFloat(skipChar) parseFloat(skipChar)\n#define getString( pre_string, post_string, buffer, length)\nreadBytesBetween( pre_string, terminator, buffer, length)\n*/\n\nclass Stream : public Print\n{\n protected:\n unsigned long _timeout; // number of milliseconds to wait for the next char before aborting timed read\n unsigned long _startMillis; // used for timeout measurement\n int timedRead(); // private method to read stream with timeout\n int timedPeek(); // private method to peek stream with timeout\n int peekNextDigit(); // returns the next numeric digit in the stream or -1 if timeout\n\n public:\n virtual int available() = 0;\n virtual int read() = 0;\n virtual int peek() = 0;\n virtual void flush() = 0;\n\n Stream() {_timeout=1000;}\n\n// parsing methods\n\n void setTimeout(unsigned long timeout); // sets maximum milliseconds to wait for stream data, default is 1 second\n\n bool find(char *target); // reads data from the stream until the target string is found\n bool find(uint8_t *target) { return find ((char *)target); }\n // returns true if target string is found, false if timed out (see setTimeout)\n\n bool find(char *target, size_t length); // reads data from the stream until the target string of given length is found\n bool find(uint8_t *target, size_t length) { return find ((char *)target, length); }\n // returns true if target string is found, false if timed out\n\n bool findUntil(char *target, char *terminator); // as find but search ends if the terminator string is found\n bool findUntil(uint8_t *target, char *terminator) { return findUntil((char *)target, terminator); }\n\n bool findUntil(char *target, size_t targetLen, char *terminate, size_t termLen); // as above but search ends if the terminate string is found\n bool findUntil(uint8_t *target, size_t targetLen, char *terminate, size_t termLen) {return findUntil((char *)target, targetLen, terminate, termLen); }\n\n\n long parseInt(); // returns the first valid (long) integer value from the current position.\n // initial characters that are not digits (or the minus sign) are skipped\n // integer is terminated by the first character that is not a digit.\n\n float parseFloat(); // float version of parseInt\n\n size_t readBytes( char *buffer, size_t length); // read chars from stream into buffer\n size_t readBytes( uint8_t *buffer, size_t length) { return readBytes((char *)buffer, length); }\n // terminates if length characters have been read or timeout (see setTimeout)\n // returns the number of characters placed in the buffer (0 means no valid data found)\n\n size_t readBytesUntil( char terminator, char *buffer, size_t length); // as readBytes with terminator character\n size_t readBytesUntil( char terminator, uint8_t *buffer, size_t length) { return readBytesUntil(terminator, (char *)buffer, length); }\n // terminates if length characters have been read, timeout, or if the terminator character detected\n // returns the number of characters placed in the buffer (0 means no valid data found)\n\n // Arduino String functions to be added here\n String readString();\n String readStringUntil(char terminator);\n\n protected:\n long parseInt(char skipChar); // as above but the given skipChar is ignored\n // as above but the given skipChar is ignored\n // this allows format characters (typically commas) in values to be ignored\n\n float parseFloat(char skipChar); // as above but the given skipChar is ignored\n\n struct MultiTarget {\n const char *str; // string you're searching for\n size_t len; // length of string you're searching for\n size_t index; // index used by the search routine.\n };\n\n // This allows you to search for an arbitrary number of strings.\n // Returns index of the target that is found first or -1 if timeout occurs.\n int findMulti(struct MultiTarget *targets, int tCount);\n};\n\n#endif\n"

},

{

"path": "arduino/opencr_arduino/opencr/cores/arduino/Tone.cpp",

"content": "/* Tone.cpp\r\n\r\n A Tone Generator Library\r\n\r\n Written by Brett Hagman\r\n\r\n This library is free software; you can redistribute it and/or\r\n modify it under the terms of the GNU Lesser General Public\r\n License as published by the Free Software Foundation; either\r\n version 2.1 of the License, or (at your option) any later version.\r\n\r\n This library is distributed in the hope that it will be useful,\r\n but WITHOUT ANY WARRANTY; without even the implied warranty of\r\n MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU\r\n Lesser General Public License for more details.\r\n\r\n You should have received a copy of the GNU Lesser General Public\r\n License along with this library; if not, write to the Free Software\r\n Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA\r\n\r\nVersion Modified By Date Comments\r\n------- ----------- -------- --------\r\n0001 B Hagman 09/08/02 Initial coding\r\n0002 B Hagman 09/08/18 Multiple pins\r\n0003 B Hagman 09/08/18 Moved initialization from constructor to begin()\r\n0004 B Hagman 09/09/26 Fixed problems with ATmega8\r\n0005 B Hagman 09/11/23 Scanned prescalars for best fit on 8 bit timers\r\n 09/11/25 Changed pin toggle method to XOR\r\n 09/11/25 Fixed timer0 from being excluded\r\n0006 D Mellis 09/12/29 Replaced objects with functions\r\n0007 M Sproul 10/08/29 Changed #ifdefs from cpu to register\r\n0008 S Kanemoto 12/06/22 Fixed for Leonardo by @maris_HY\r\n0009 J Reucker 15/04/10 Issue #292 Fixed problems with ATmega8 (thanks to Pete62)\r\n0010 jipp 15/04/13 added additional define check #2923\r\n0011 Baram 16/10/06 fixed for OpenCR\r\n*************************************************/\r\n\r\n#include \r\n#include \"variant.h\"\r\n#include \"Tone.h\"\r\n\r\n\r\n// timerx_toggle_count:\r\n// > 0 - duration specified\r\n// = 0 - stopped\r\n// < 0 - infinitely (until stop() method called, or new play() called)\r\n\r\nvolatile int32_t tone_toggle_count;\r\nvolatile uint8_t tone_timer = TIMER_TONE;\r\nvolatile uint8_t tone_pin;\r\nvolatile uint8_t tone_pin_out;\r\nvolatile bool tone_enable = false;\r\n\r\n\r\nvoid tone_isr( void );\r\n\r\n\r\n\r\nstatic void toneBegin(uint8_t _pin)\r\n{\r\n tone_pin = _pin;\r\n tone_pin_out = 0;\r\n tone_enable = true;\r\n}\r\n\r\n\r\nstatic void toneEnd(void)\r\n{\r\n tone_enable = false;\r\n tone_pin_out = 0;\r\n drv_timer_pause(tone_timer);\r\n}\r\n\r\n\r\n// frequency (in hertz) and duration (in milliseconds).\r\n\r\nvoid tone(uint8_t _pin, unsigned int frequency, unsigned long duration)\r\n{\r\n //uint8_t prescalarbits = 0b001;\r\n long toggle_count = 0;\r\n uint32_t ocr = 0;\r\n //int8_t _timer;\r\n\r\n\r\n // Set the pinMode as OUTPUT\r\n pinMode(_pin, OUTPUT);\r\n digitalWrite(_pin, 0);\r\n\r\n ocr = (1000000 / frequency) / 2 ;\r\n\r\n // Calculate the toggle count\r\n if (duration > 0)\r\n {\r\n toggle_count = 2 * frequency * duration / 1000;\r\n }\r\n else\r\n {\r\n toggle_count = -1;\r\n }\r\n\r\n tone_toggle_count = toggle_count;\r\n\r\n toneBegin(_pin);\r\n\r\n drv_timer_set_period(tone_timer, ocr);\r\n drv_timer_attachInterrupt(tone_timer, tone_isr);\r\n drv_timer_resume(tone_timer);\r\n}\r\n\r\n\r\nvoid noTone(uint8_t _pin)\r\n{\r\n toneEnd();\r\n digitalWrite(_pin, 0);\r\n}\r\n\r\n\r\nvoid tone_isr( void )\r\n{\r\n if (tone_toggle_count != 0)\r\n {\r\n // toggle the pin\r\n tone_pin_out ^= 1;\r\n digitalWrite(tone_pin, tone_pin_out);\r\n\r\n if(tone_toggle_count > 0)\r\n {\r\n tone_toggle_count--;\r\n }\r\n }\r\n else\r\n {\r\n toneEnd();\r\n }\r\n}\r\n"

},

{

"path": "arduino/opencr_arduino/opencr/cores/arduino/Tone.h",

"content": "/*\n Copyright (c) 2011 Arduino. All right reserved.\n\n This library is free software; you can redistribute it and/or\n modify it under the terms of the GNU Lesser General Public\n License as published by the Free Software Foundation; either\n version 2.1 of the License, or (at your option) any later version.\n\n This library is distributed in the hope that it will be useful,\n but WITHOUT ANY WARRANTY; without even the implied warranty of\n MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. \n See the GNU Lesser General Public License for more details.\n\n You should have received a copy of the GNU Lesser General Public\n License along with this library; if not, write to the Free Software\n Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA\n*/\n\n#ifndef _WIRING_TONE_\n#define _WIRING_TONE_\n\n\n#endif /* _WIRING_TONE_ */\n"

},

{

"path": "arduino/opencr_arduino/opencr/cores/arduino/UARTClass.cpp",

"content": "/*\r\n Copyright (c) 2011 Arduino. All right reserved.\r\n\r\n This library is free software; you can redistribute it and/or\r\n modify it under the terms of the GNU Lesser General Public\r\n License as published by the Free Software Foundation; either\r\n version 2.1 of the License, or (at your option) any later version.\r\n\r\n This library is distributed in the hope that it will be useful,\r\n but WITHOUT ANY WARRANTY; without even the implied warranty of\r\n MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE.\r\n See the GNU Lesser General Public License for more details.\r\n\r\n You should have received a copy of the GNU Lesser General Public\r\n License along with this library; if not, write to the Free Software\r\n Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA\r\n*/\r\n\r\n#include \r\n#include \r\n#include \r\n#include \"UARTClass.h\"\r\n#include \"wiring_digital.h\"\r\n#include \"wiring_constants.h\"\r\n#include \"variant.h\"\r\n#include \"digitalWriteFast.h\"\r\n// Constructors ////////////////////////////////////////////////////////////////\r\nUARTClass::UARTClass(void){\r\n\r\n}\r\n\r\nUARTClass::UARTClass(uint8_t uart_num, uint8_t uart_mode, uint8_t *txBuffer, uint16_t tx_buffer_size)\r\n{\r\n _uart_num = uart_num;\r\n _uart_mode = uart_mode;\r\n _uart_baudrate = 0;\r\n rx_cnt = 0;\r\n tx_cnt = 0;\r\n tx_write_size = 0;\r\n tx_buffer.buffer = txBuffer;\r\n tx_buffer.buffer_size = tx_buffer_size;\r\n}\r\n\r\nvoid UARTClass::begin(const uint32_t dwBaudRate)\r\n{\r\n begin(dwBaudRate, Mode_8N1);\r\n}\r\n\r\nvoid UARTClass::begin(const uint32_t dwBaudRate, const UARTModes config)\r\n{\r\n UNUSED(config);\r\n\r\n#ifdef DRV_UART_RX_DMA_ONLY\r\n rx_buffer.iHead = rx_buffer.iTail = 0;\r\n#endif\r\n tx_buffer.iHead = 0;\r\n tx_buffer.iTail = 0;\r\n\r\n _uart_baudrate = dwBaudRate;\r\n\r\n drv_uart_begin(_uart_num, _uart_mode, dwBaudRate);\r\n}\r\n\r\nvoid UARTClass::end( void )\r\n{\r\n // Clear any received data\r\n#ifdef DRV_UART_RX_DMA_ONLY\r\n rx_buffer.iHead = rx_buffer.iTail;\r\n#endif\r\n // Wait for any outstanding data to be sent\r\n flush();\r\n}\r\n\r\nint UARTClass::available( void )\r\n{\r\n#ifdef DRV_UART_RX_DMA_ONLY\r\n if(drv_uart_get_mode(_uart_num) == DRV_UART_IRQ_MODE )\r\n {\r\n return (uint32_t)(SERIAL_BUFFER_SIZE + rx_buffer.iHead - rx_buffer.iTail) % SERIAL_BUFFER_SIZE;\r\n }\r\n else\r\n {\r\n return drv_uart_available(_uart_num);\r\n }\r\n#else\r\n return drv_uart_available(_uart_num);\r\n#endif \r\n}\r\n\r\nint UARTClass::availableForWrite(void)\r\n{\r\n int head = tx_buffer.iHead;\r\n int tail = tx_buffer.iTail;\r\n if (head >= tail) return SERIAL_BUFFER_SIZE - 1 - head + tail;\r\n return tail - head - 1;\r\n}\r\n\r\nint UARTClass::peek( void )\r\n{\r\n#ifdef DRV_UART_RX_DMA_ONLY\r\n if(drv_uart_get_mode(_uart_num) == DRV_UART_IRQ_MODE )\r\n {\r\n if ( rx_buffer.iHead == rx_buffer.iTail )\r\n return -1;\r\n\r\n return rx_buffer.buffer[rx_buffer.iTail];\r\n }\r\n else \r\n {\r\n return drv_uart_peek(_uart_num);\r\n }\r\n#else\r\n return drv_uart_peek(_uart_num);\r\n#endif \r\n}\r\n\r\nint UARTClass::read( void )\r\n{\r\n#ifdef DRV_UART_RX_DMA_ONLY\r\n if(drv_uart_get_mode(_uart_num) == DRV_UART_IRQ_MODE )\r\n {\r\n // if the head isn't ahead of the tail, we don't have any characters\r\n if ( rx_buffer.iHead == rx_buffer.iTail )\r\n return -1;\r\n\r\n uint8_t uc = rx_buffer.buffer[rx_buffer.iTail];\r\n rx_buffer.iTail = (unsigned int)(rx_buffer.iTail + 1) % SERIAL_BUFFER_SIZE;\r\n rx_cnt++;\r\n return uc;\r\n }\r\n else\r\n {\r\n int return_value = drv_uart_read(_uart_num);\r\n if (return_value != -1) \r\n {\r\n rx_cnt++;\r\n }\r\n return return_value; \r\n }\r\n#else\r\n int return_value = drv_uart_read(_uart_num);\r\n if (return_value != -1) \r\n {\r\n rx_cnt++;\r\n }\r\n return return_value; \r\n#endif \r\n}\r\n\r\nvoid UARTClass::flush( void )\r\n{\r\n while (tx_write_size); //wait for transmit data to be sent\r\n}\r\n\r\nvoid UARTClass::flushRx( uint32_t timeout_ms )\r\n{\r\n#ifdef DRV_UART_RX_DMA_ONLY\r\n if(drv_uart_get_mode(_uart_num) == DRV_UART_IRQ_MODE )\r\n {\r\n // sort of hack, wait the time specified and then just clear it\r\n if (timeout_ms) \r\n {\r\n uint32_t pre_time_ms = millis();\r\n while((millis() - pre_time_ms) < timeout_ms)\r\n {\r\n }\r\n\r\n }\r\n rx_buffer.iTail = rx_buffer.iHead; // clear out buffer\r\n }\r\n else \r\n {\r\n drv_uart_rx_flush(_uart_num, timeout_ms);\r\n }\r\n#else\r\n drv_uart_rx_flush(_uart_num, timeout_ms);\r\n#endif \r\n}\r\n\r\nsize_t UARTClass::write( const uint8_t uc_data )\r\n{\r\n return write(&uc_data, 1); // Lets call the buffer function to do the main work\r\n}\r\nvoid inline UARTClass::startNextTransmitDMAorIT()\r\n{\r\n tx_write_size = (tx_buffer.iTail < tx_buffer.iHead)? tx_buffer.iHead-tx_buffer.iTail : tx_buffer.buffer_size - tx_buffer.iTail;\r\n if (drv_uart_write_dma_it(_uart_num, &tx_buffer.buffer[tx_buffer.iTail], tx_write_size) != 0) \r\n {\r\n tx_write_size = 0; // error so clear it out\r\n }\r\n}\r\n\r\nsize_t UARTClass::write( const uint8_t *buffer, size_t size )\r\n{\r\n tx_cnt += size;\r\n size_t cbLeft = size; \r\n\r\n // Lets try to put as much of this data into our TX buffer as possible. \r\n while (cbLeft--) \r\n {\r\n uint16_t nextWrite = (tx_buffer.iHead + 1) % tx_buffer.buffer_size;\r\n if (tx_buffer.iTail == nextWrite) \r\n {\r\n // See if we have an active TX or not\r\n if (!tx_write_size)\r\n {\r\n startNextTransmitDMAorIT();\r\n }\r\n // right now this will wait for the entire previous write to complete before continue...\r\n while (tx_buffer.iTail == nextWrite) \r\n {\r\n\r\n }\r\n }\r\n tx_buffer.buffer[tx_buffer.iHead] = *buffer++;\r\n tx_buffer.iHead = nextWrite;\r\n\r\n }\r\n // we finished putting stuff on queue, so see if we need to start up write\r\n // or if it is already going. \r\n if (!tx_write_size)\r\n {\r\n startNextTransmitDMAorIT();\r\n }\r\n return size; \r\n}\r\n\r\n\r\nuint32_t UARTClass::getBaudRate( void )\r\n{\r\n return _uart_baudrate;\r\n}\r\n\r\nuint32_t UARTClass::getRxCnt(void)\r\n{\r\n return rx_cnt;\r\n}\r\n\r\nuint32_t UARTClass::getTxCnt(void)\r\n{\r\n return tx_cnt;\r\n}\r\n\r\n\r\nvoid UARTClass::RxHandler (void)\r\n{\r\n#ifdef DRV_UART_RX_DMA_ONLY\r\n if( _uart_mode == DRV_UART_IRQ_MODE )\r\n {\r\n\r\n if(available() < (SERIAL_BUFFER_SIZE - 1))\r\n {\r\n drv_uart_read_buf(_uart_num, &r_byte, 1);\r\n rx_buffer.buffer[rx_buffer.iHead] = r_byte;\r\n \t\trx_buffer.iHead = (uint16_t)(rx_buffer.iHead + 1) % SERIAL_BUFFER_SIZE;\r\n }\r\n drv_uart_start_rx(_uart_num);\r\n }\r\n#endif\r\n}\r\n\r\nvoid UARTClass::TxHandler(void)\r\n{\r\n // We completed previous write, so update our tail pointer by count\r\n tx_buffer.iTail += tx_write_size; \r\n if (tx_buffer.iTail >= tx_buffer.buffer_size) \r\n tx_buffer.iTail = 0; // Should only wrap to start by our other stuff...\r\n\r\n if (tx_buffer.iHead != tx_buffer.iTail)\r\n {\r\n startNextTransmitDMAorIT();\r\n }\r\n else \r\n {\r\n // finished all outstanding writes so lets set count to 0\r\n tx_write_size = 0;\r\n }\r\n}\r\n"

},

{

"path": "arduino/opencr_arduino/opencr/cores/arduino/UARTClass.h",

"content": "/*\r\n Copyright (c) 2011 Arduino. All right reserved.\r\n\r\n This library is free software; you can redistribute it and/or\r\n modify it under the terms of the GNU Lesser General Public\r\n License as published by the Free Software Foundation; either\r\n version 2.1 of the License, or (at your option) any later version.\r\n\r\n This library is distributed in the hope that it will be useful,\r\n but WITHOUT ANY WARRANTY; without even the implied warranty of\r\n MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE.\r\n See the GNU Lesser General Public License for more details.\r\n\r\n You should have received a copy of the GNU Lesser General Public\r\n License along with this library; if not, write to the Free Software\r\n Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA\r\n*/\r\n\r\n#ifndef _UART_CLASS_\r\n#define _UART_CLASS_\r\n\r\n#include \"HardwareSerial.h\"\r\n#include \r\n\r\n\r\n#define SERIAL_8N1 UARTClass::Mode_8N1\r\n#define SERIAL_8E1 UARTClass::Mode_8E1\r\n#define SERIAL_8O1 UARTClass::Mode_8O1\r\n#define SERIAL_8M1 UARTClass::Mode_8M1\r\n#define SERIAL_8S1 UARTClass::Mode_8S1\r\n\r\n#define SERIAL_BUFFER_SIZE 2048\r\n#define SERIAL_WRITES_NON_BLOCKING 1\r\nclass UARTClass : public HardwareSerial\r\n{\r\n public:\r\n enum UARTModes {\r\n Mode_8N1 = 0, // = US_MR_CHRL_8_BIT | US_MR_NBSTOP_1_BIT | UART_MR_PAR_NO,\r\n Mode_8E1, // = US_MR_CHRL_8_BIT | US_MR_NBSTOP_1_BIT | UART_MR_PAR_EVEN,\r\n Mode_8O1, // = US_MR_CHRL_8_BIT | US_MR_NBSTOP_1_BIT | UART_MR_PAR_ODD,\r\n Mode_8M1, // = US_MR_CHRL_8_BIT | US_MR_NBSTOP_1_BIT | UART_MR_PAR_MARK,\r\n Mode_8S1 // = US_MR_CHRL_8_BIT | US_MR_NBSTOP_1_BIT | UART_MR_PAR_SPACE,\r\n };\r\n UARTClass(uint8_t uart_num, uint8_t uart_mode, uint8_t *txBuffer, uint16_t tx_buffer_size);\r\n UARTClass(void);\r\n void begin(const uint32_t dwBaudRate);\r\n void begin(const uint32_t dwBaudRate, const UARTModes config);\r\n void end(void);\r\n int available(void);\r\n int availableForWrite(void);\r\n int peek(void);\r\n int read(void);\r\n void flush(void);\r\n void flushRx( uint32_t timeout_ms );\r\n size_t write(const uint8_t c);\r\n size_t write(const uint8_t *buffer, size_t size); \r\n using Print::write; // pull in write(str) and write(buf, size) from Print\r\n\r\n\r\n void RxHandler(void); /* Vassilis Serasidis */\r\n void TxHandler(void); /* Vassilis Serasidis */\r\n uint32_t getBaudRate(void);\r\n\r\n uint32_t getRxCnt(void);\r\n uint32_t getTxCnt(void);\r\n\r\n operator bool() { return true; }; // UART always active\r\n\r\n\r\n protected:\r\n void inline startNextTransmitDMAorIT(void);\r\n#ifdef DRV_UART_RX_DMA_ONLY\r\n struct ring_buffer\r\n {\r\n uint8_t buffer[SERIAL_BUFFER_SIZE];\r\n volatile uint16_t iHead;\r\n volatile uint16_t iTail;\r\n };\r\n#endif \r\n struct tx_no_cache_buffer \r\n {\r\n uint8_t *buffer;\r\n uint16_t buffer_size;\r\n volatile uint16_t iHead;\r\n volatile uint16_t iTail;\r\n };\r\n\r\n uint8_t _uart_num;\r\n uint8_t _uart_mode;\r\n uint32_t _uart_baudrate;\r\n\r\n uint8_t r_byte;\r\n volatile uint16_t tx_write_size;\r\n tx_no_cache_buffer tx_buffer;\r\n#ifdef DRV_UART_RX_DMA_ONLY\r\n ring_buffer rx_buffer;\r\n#endif\r\n uint32_t rx_cnt;\r\n uint32_t tx_cnt;\r\n};\r\n\r\n#endif // _UART_CLASS_\r\n"

},

{

"path": "arduino/opencr_arduino/opencr/cores/arduino/USBSerial.cpp",

"content": "/****************************************************************************\r\n *\r\n * USBSerial core library for Arduino STM32 + HAL + CubeMX (HALMX).\r\n *\r\n * Copyright (c) 2016 by Vassilis Serasidis \r\n * Home: http://www.serasidis.gr\r\n * email: avrsite@yahoo.gr\r\n *\r\n * Arduino_STM32 forum: http://www.stm32duino.com\r\n *\r\n * Permission to use, copy, modify, and/or distribute this software for\r\n * any purpose with or without fee is hereby granted, provided that the\r\n * above copyright notice and this permission notice appear in all copies.\r\n *\r\n * Some functions follow the sam and samd arduino core libray files.\r\n *\r\n * THE SOFTWARE IS PROVIDED \"AS IS\" AND THE AUTHOR DISCLAIMS ALL\r\n * WARRANTIES WITH REGARD TO THIS SOFTWARE INCLUDING ALL IMPLIED\r\n * WARRANTIES OF MERCHANTABILITY AND FITNESS. IN NO EVENT SHALL THE AUTHOR\r\n * BE LIABLE FOR ANY SPECIAL, DIRECT, INDIRECT, OR CONSEQUENTIAL DAMAGES\r\n * OR ANY DAMAGES WHATSOEVER RESULTING FROM LOSS OF USE, DATA OR PROFITS,\r\n * WHETHER IN AN ACTION OF CONTRACT, NEGLIGENCE OR OTHER TORTIOUS ACTION,\r\n * ARISING OUT OF OR IN CONNECTION WITH THE USE OR PERFORMANCE OF THIS\r\n *\r\n ****************************************************************************/\r\n/*\r\n * Modified on: 2016. 7.12.\r\n * Author: Baram, PBHP\r\n */\r\n\r\n#include \r\n\r\n#include \r\n#include \"variant.h\"\r\n\r\n\r\nextern uint32_t usb_cdc_bitrate;\r\nextern uint32_t usb_cdc_debug_cnt[];\r\n\r\n\r\nUSBSerial::USBSerial(){\r\n baudrate = 0;\r\n rx_cnt = 0;\r\n tx_cnt = 0;\r\n rx_err_cnt = 0;\r\n tx_err_cnt = 0;\r\n}\r\n\r\nvoid USBSerial::begin(uint32_t baud_count){\r\n UNUSED(baud_count);\r\n}\r\n\r\nvoid USBSerial::begin(uint32_t baud_count, uint8_t config){\r\n UNUSED(baud_count);\r\n UNUSED(config);\r\n}\r\n\r\nvoid USBSerial::end(void){\r\n}\r\n\r\n\r\nint USBSerial::available(void){\r\n return vcp_is_available();\r\n}\r\n\r\nint USBSerial::peek(void)\r\n{\r\n return vcp_peek();\r\n}\r\n\r\nint USBSerial::read(void)\r\n{\r\n if ( vcp_is_available() == 0 )\r\n return -1;\r\n\r\n rx_cnt++;\r\n\r\n return vcp_getch();\r\n}\r\n\r\nvoid USBSerial::flush(void){\r\n while( vcp_is_transmitted() == FALSE );\r\n}\r\n\r\nsize_t USBSerial::write(const uint8_t *buffer, size_t size)\r\n{\r\n uint32_t length;\r\n\r\n length = vcp_write((uint8_t *)buffer, (uint32_t)size);\r\n\r\n tx_cnt += length;\r\n \r\n return (size_t)length;\r\n}\r\n\r\n\r\nsize_t USBSerial::write(uint8_t c) {\r\n\treturn write(&c, 1);\r\n}\r\n\r\nuint32_t USBSerial::getBaudRate(void)\r\n{\r\n return usb_cdc_bitrate;\r\n}\r\n\r\nuint32_t USBSerial::getRxCnt(void)\r\n{\r\n return rx_cnt;\r\n}\r\n\r\nuint32_t USBSerial::getTxCnt(void)\r\n{\r\n return tx_cnt;\r\n}\r\n\r\nuint32_t USBSerial::getRxErrCnt(void)\r\n{\r\n return usb_cdc_debug_cnt[0];\r\n}\r\n\r\nuint32_t USBSerial::getTxErrCnt(void)\r\n{\r\n return usb_cdc_debug_cnt[1];\r\n}\r\n\r\n\r\n// This operator is a convenient way for a sketch to check whether the\r\n// port has actually been configured and opened by the host (as opposed\r\n// to just being connected to the host). It can be used, for example, in\r\n// setup() before printing to ensure that an application on the host is\r\n// actually ready to receive and display the data.\r\n// We add a short delay before returning to fix a bug observed by Federico\r\n// where the port is configured (lineState != 0) but not quite opened.\r\nUSBSerial::operator bool()\r\n{\r\n if( vcp_is_connected() == TRUE ) return true;\r\n else return false;\r\n}\r\n"

},

{

"path": "arduino/opencr_arduino/opencr/cores/arduino/USBSerial.h",